d触发器芯片(d触发器芯片接线图)

今天给大家分享一下D触发器芯片的知识,同时也讲解一下D触发器芯片的接线图。如果你碰巧解决了你现在面临的问题,别忘了关注这个网站,现在就开始!

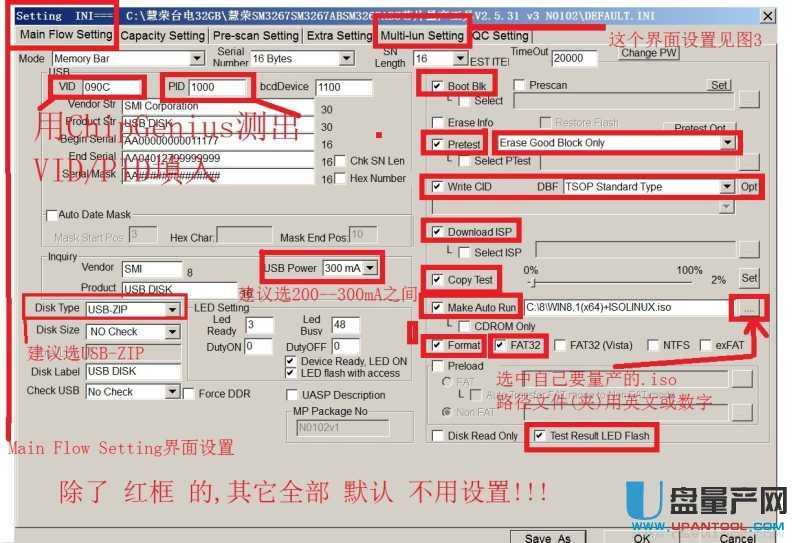

用双D触发器芯片设计了一种异步四进制加法计数器。

两个D触发器的R端和S端都接VCC,可以改成。

仅异步设置/PRE1和/PRE2,异步清除/CLR1和/CLR2。

触发器的异步端一般指异步清零端或异步置位端。

与同步清算终端或同步设定终端相比,它们之间的区别如下:

同步清零或置位,电平有效后,清零或置位操作发生在时钟的上升沿(或下降沿);

异步清零或置位,只要电平有效,清零或置位就会立即发生。

异步二进制加法计数器

异步二进制计数器从低位到高位逐位进行加法计数。因此,触发器是不同步的。根据二进制加法的计数规则,如果第I位为1,则加1时应变为0,同时向高位发送进位信号使其翻转。如果用T '触发器构成计数器电路,只需将低触发器的Q(或Q)连接到高触发器的时钟输入端即可实现进位。

百度百科-异步计数器

是什么芯片?

是一个D触发器,功能很多,可以用作双稳态、寄存器、移位寄存器、振荡器、单稳态、分频器等。

d触发器是一种具有记忆功能和两种稳定状态的信息存储器件。它是各种时序电路最基本的逻辑单元,是数字逻辑电路中重要的单元电路。

因此,D触发器广泛应用于数字系统和计算机中。触发器有两个稳定状态,即“0”和“1”,在一些外部信号的作用下,可以从一个稳定状态翻转到另一个稳定状态。

d触发器有一个由集成触发器和门电路组成的触发器。有两种触发模式:电平触发和边沿触发。前者可以在CP(时钟脉冲)=1时触发,后者可以在CP前沿触发(正跃迁0→1)。

D触发器的二级状态取决于触发前D端的状态,即二级状态= D .因此,它具有置0和置1两种功能。

对于edge D触发器,由于电路具有CP=1时保持阻塞的功能,所以CP=1时D端的数据状态发生变化,不会影响触发器的输出状态。

d触发器应用广泛,可用作数字信号寄存器、移位寄存器、分频器和波形发生器。

结构

d触发器(数据触发器或延迟触发器)由四个与非门组成,其中G1和G2构成基本的RS触发器。电平触发的主从触发器工作时,输入信号必须加在正跳变沿之前。如果在CP高电平期间输入端有干扰信号,则触发器的状态可能是错误的。

边沿触发允许在CP触发边沿到达之前添加输入信号。这大大缩短了输入干扰的时间,降低了干扰的可能性。边沿d触发器也称为保持模块边沿d触发器。Edge D触发器可以由两个D触发器串联组成,但之一个D触发器的CP需要非门反转。

下降沿D触发器芯片主要有哪些类型?

下降沿D触发器芯片主要类型有和,双D触发器和,八D触发器(三态)7474,74H74,74F74,,,,和74C74,双D正沿。JK触发器(如)是下降沿触发,一般D触发器芯片()是上升沿触发。

D触发器芯片的介绍到此结束。感谢您花时间阅读本网站的内容。别忘了在这个网站上搜索更多关于D触发器芯片布线图和D触发器芯片的信息。