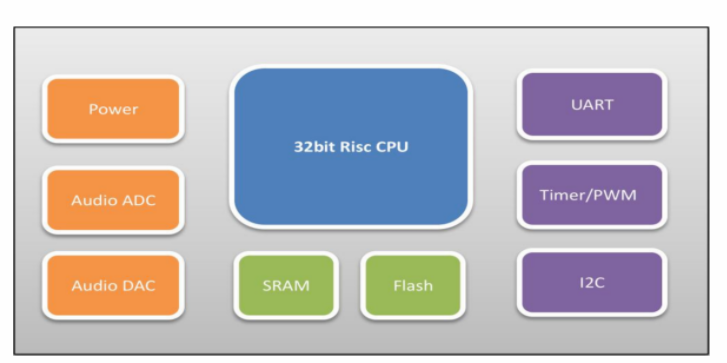

基于FPGA的串口传图SDRAM缓存VGA显示

简介

在DE2开发板上,使用串口接收PC上的Qt程序发送的640*480彩色图片,以格式存入SDRAM,通过VGA显示在屏幕上。

开发板:DE2

开发工具: II 13.0 + 10.5 SE

全局时钟:50M

VGA时钟:25M

SDRAM时钟:100M

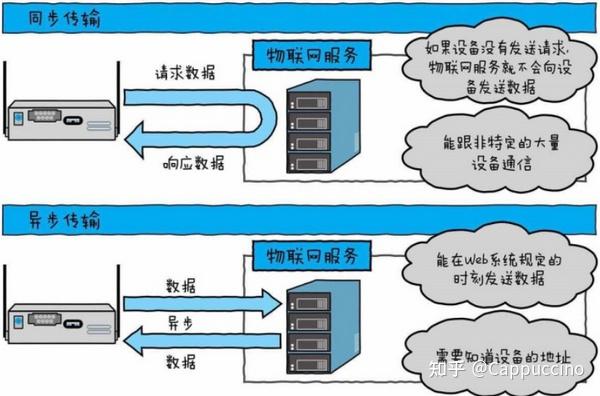

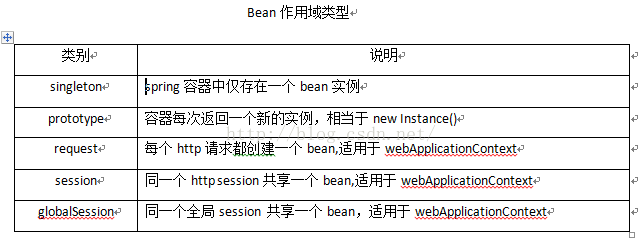

总体结构

上图是系统的总体结构,省略了PLL模块,实际上两个fifo都在SDRAM控制器内部。

一共5个模块:PLL、串口接收、数据合并、SDRAM控制器、VGA控制器

模块介绍

PLL模块负责生成三路时钟:

串口接收模块

波特率:

数据位:8

校验:无

停止位:1

串口模块负责接收PC发送的数据。

串口模块还是用之前的,不做修改。接口如下:

module uart_rx(input clk,input rst_n,// uart rxinput rx,// output data & validoutput reg valid,output reg [7:0] data

);

数据合并模块

由于使用格式存储彩色图片,所以要把串口接收到的单字节数据合并为16bit位宽的格式数据。接口如下:

module data_merge(input clk,input rst_n,// input data & validinput iValid,input [7:0] iData,// output data & validoutput reg oValid,output reg [15:0] oData

);

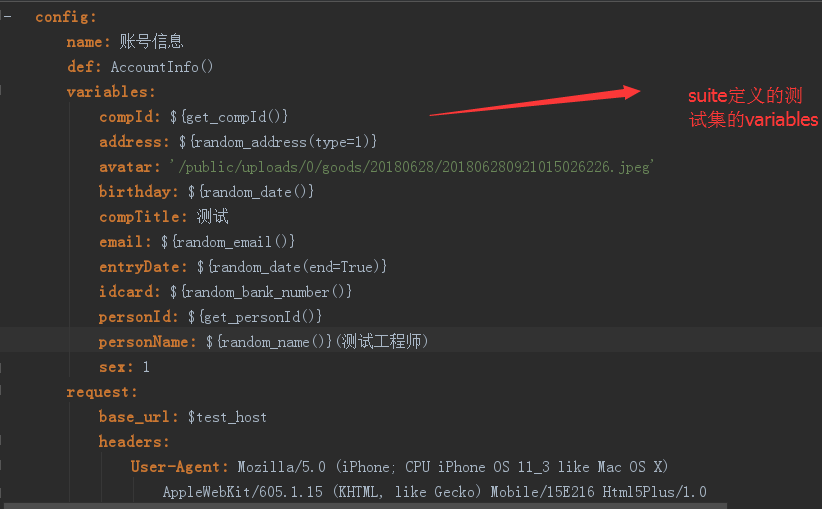

sdram控制器模块

SDRAM控制器模块负责存储图片,该SDRAM控制器是大佬写的,不过其本质上是根据友晶提供的SDRAM控制器改良的,咱要站在巨人的肩膀上前行。接口如下:

module Sdram_Control_2Port(// HOST Sideinput REF_CLK; //sdram control clockinput OUT_CLK; //sdram output clockinput RESET_N; //System Reset// FIFO Write Side 1input [`DSIZE-1:0] WR_DATA; //Data inputinput WR; //Write Requestinput [`ASIZE-1:0] WR_MIN_ADDR; //Write start addressinput [`ASIZE-1:0] WR_MAX_ADDR; //Write max addressinput [8:0] WR_LENGTH; //Write lengthinput WR_LOAD; //Write register load & fifo clearinput WR_CLK; //Write fifo clock// FIFO Read Side 1output [`DSIZE-1:0] RD_DATA; //Data outputinput RD; //Read Requestinput [`ASIZE-1:0] RD_MIN_ADDR; //Read start addressinput [`ASIZE-1:0] RD_MAX_ADDR; //Read max addressinput [8:0] RD_LENGTH; //Read lengthinput RD_LOAD; //Read register load & fifo clearinput RD_CLK; //Read fifo clock//STATUS Sideoutput busy;// SDRAM Sideoutput [`ROWSIZE-1:0] SA; //SDRAM address outputoutput [1:0] BA; //SDRAM bank addressoutput CS_N; //SDRAM Chip Selectsoutput CKE; //SDRAM clock enableoutput RAS_N; //SDRAM Row address Strobeoutput CAS_N; //SDRAM Column address Strobeoutput WE_N; //SDRAM write enableinout [`DSIZE-1:0] DQ; //SDRAM data busoutput [`DSIZE/8-1:0] DQM; //SDRAM data mask linesoutput SDR_CLK; //SDRAM clock

);

VGA控制器模块

VGA控制器负责产生VGA时序,驱动显示屏。

使用友晶资料盘里面的VGA控制器。接口如下:

module VGA_Ctrl (// Host Sideinput [7:0] iRed;input [7:0] iGreen;input [7:0] iBlue;output [20:0] oAddress;output [10:0] oCurrent_X;output [10:0] oCurrent_Y;output oRequest;// VGA Sideoutput [7:0] oVGA_R;output [7:0] oVGA_G;output [7:0] oVGA_B;output reg oVGA_HS;output reg oVGA_VS;output oVGA_SYNC;output oVGA_BLANK;output oVGA_CLOCK;// Control Signalinput iCLK;input iRST_N;

);

顶层模块例化上面这些模块即可。

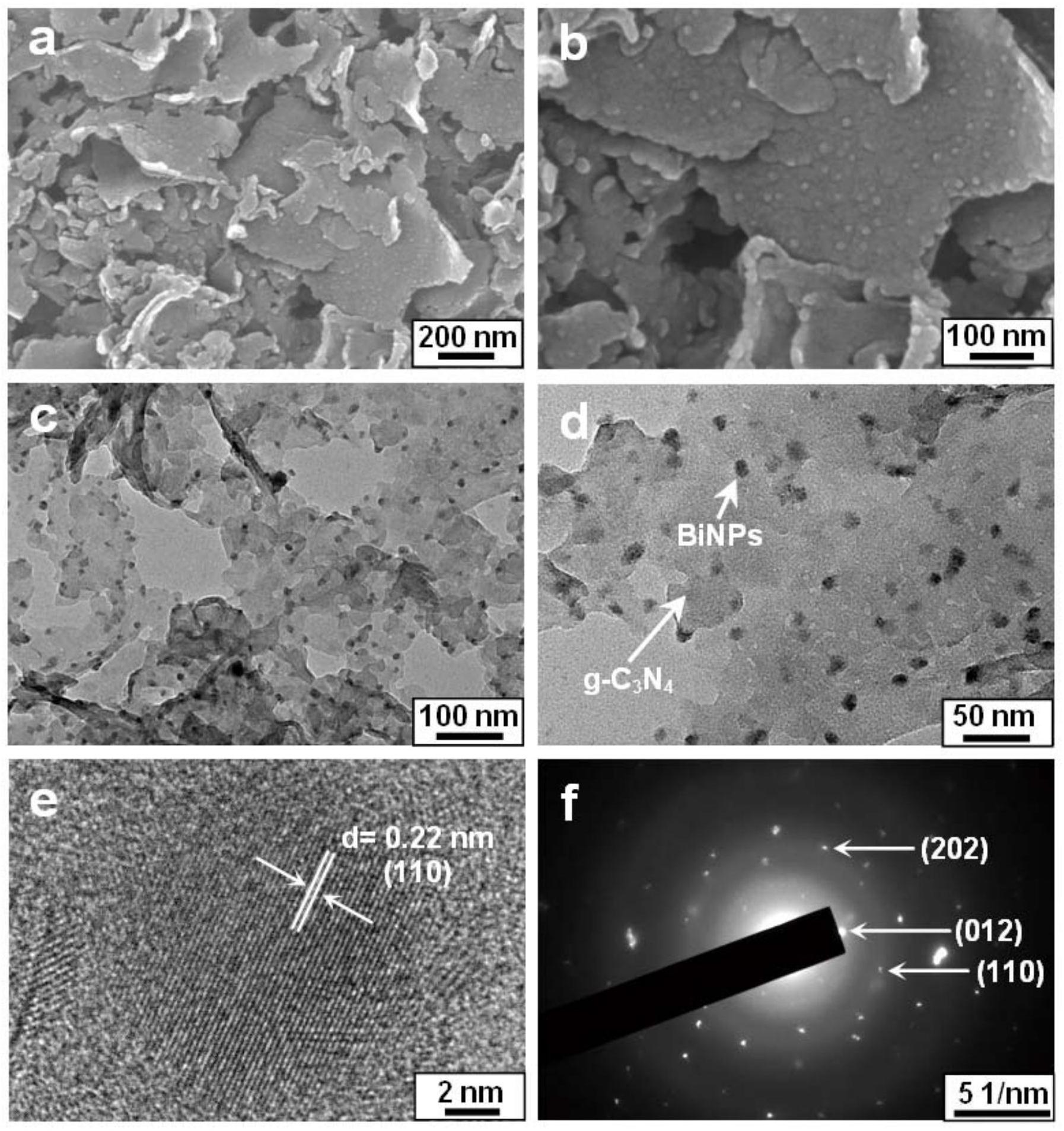

Qt上位机程序

自己用Qt写了一个串口传图程序,可以读取640*480分辨率的彩色图片,将格式的图片转,再通过串口发送,如图:

效果演示

fpga串口传图