PCIe 每日一问一答

以下转载自【毅力挑战】PCIe 每日一问一答(2022.03 归档)-阿里云开发者社区

一位有毅力的大神

2022.03.01 - PCIe 是什么?

随着 PCIe 的迭代,传输速率越来越高,高速信号传输中的信号衰减问题越来越大。目前解决信号衰减的三大方案:① 高速 PCB 板材;② ;③ 。 是三者中性价比最高的一种方案,也更为主流。2021年是 发展元年。

通过 其 Rx 端 CTLE/DFE (连续时间线性均衡/判断反馈均衡) 、CDR (时钟数据恢复) 及 Tx 端 EQ (均衡),来够补偿信道损耗,消除信号抖动,提升信号完整性,从而增加传输距离。

是放大信号, 是重新生成信号。 比 性能更高,但时延也更大。

友情链接:

PCIe Base Spec R6.0, 4.3

均衡器EQ和它在高速外部总线中的应用

和简介

PCIe 是个什么样的市场?

2022.03.02 - PCIe Lane-Lane Skew 产生的原因 及 De-skew 方法?

同一 Link 多条 Lane 之间难免存在 Skew,即便 Tx 端采用同一 Clock 同时发送,不同 Lane 上到达 Rx 时间也难以相同。PCIe Lane-Lane Skew 一般源于以下几点:

电气 及 之间存在差异。

印刷线路板阻抗变化。

不同 Lane 的走线长度存在差异。

Gen1/Gen2 时常用检测 OS 序列中的 COM 符号来实现多 Lane 的 De-skew;Gen3及以上常采用检测 SDSOS、EIEOS、SKP等方式来实现 De-skew,具体情况需具体分析。

2022.03.03 - Link Error 包括哪几种?发生 Link Error 时是如何恢复的?

Link Error,链路错误,是指连接两个 PCIe 设备的物理链路出现错误,通常在物理层检测出并传达到数据链路层。Link Error 包括以下几种:8b/10b 解码错误、 出错、符号/Block 锁定后失锁、弹性缓存上下溢出及 Lane 间消抖失败。

如果是在链路 期间发生链路错误(非 、状态),无需特殊操作,LTSSM 正常运转,各个状态的 机制保证 LTSSM 回转到 状态进行 。

如果是在 L0 状态发生链路错误(frame error等),可以由软件控制 LTSSM 由 L0 -> 进行链路恢复,或者重新训练。需要注意的是,出现链路错误后,下游设备是无法通过错误链路告知上游设备的,需要由错误链路上游的交换开关 USP 或 RC 上报错误,开启 。软件通过查验相关寄存器确认是否训练成功。

2022.03.04 - 是什么 ? 跟 TS的关系?

为了扩展 PCIe 设备的适用范围,PCIe 5.0 开始支持 。 是指运行在 PCIe PHY 上的非标准 PCIe 协议,目前有 CXL 协议。

CXL 运行在 PCIe 5.0 PHY 上,支持 CXL 协议的设备也支持 PCIe 协议。那么到底采用 CXL 还是 PCIe 协议,收发端在进行链路训练的时候可以进行协商,即 。 采用 TS1/2,跟 Cfg..Wait、Cfg..、Cfg. 并行, EQ。可参考 2022.02.21 TS 相关介绍。

勘误:

2022.02.21 , 协商与 lane 协商并行。

2022.02.15,添加参考文献

2022.03.05 - PCIe 有哪几种传输模式?

PCIe 传输 TLP 有两种模式:① Store & ;② Cut-。

Store & ,接收报文并进行校验,如有错误走 NAK DLLP 请求重传,否则推送到 Port。这种模式保证送到 出口的报文是正确的,但也因此增加了延时。对于 Data 比较大的 TLP,采用该模式时延很大。

Cut-,直接了当,接收报文直接推给 Port,没收完也推,延时低但不保证报文正确。当接收完报文进行校验,发现报文错了,发送 NAK DLLP 给 请求重传,然后给 发送 EDB(End Bad)让 无视该报文(如下图)。当链路质量不好时,频繁出现校验失败,采用该模式很浪费带宽。

▲ 图1 Cut‐ Mode Error

参考:

PCI , .inc, 10

STORE & AND CUT-

2022.03.06 - TLP 是什么?是干啥的?

Data 或称 Error ,是一种事务层报告错误的方法,报告错误时发送的 TLP 为 TLP。 TLP,有毒的 TLP,仅用于含有 Data 的 或 ,比如 写请求、MsgD、读完成、 请求及完成。

TLP 通过 TLP 中的 EP 位来指示,EP=1 时,即表示当前 TLP 数据被破坏了。注意,是 TLP Data 被破坏了,不是, 出错可不归他管, 出错那就是另外的故事了。 TLP 用于控制 Error 在整个系统内的传播,协助软件诊断该 TLP 路由路径上的 是否给该 TLP 贴上了有毒标签。

在生成这个 TLP 的时候就知道这是个 Data 错误的 TLP。既然知道 Data 出错,为什么还要继续发?—— 以读请求为例, 发出读请求后,在等待 ,现在数据读回传了,但是 在半路就检测到 Data 出错了,你这 还要不要继续发?不发的话, 还在等,直到 。倒不如给个错误信号,至少不会让 久等。 收到 TLP,知道发生了事务层错误,至于这数据要不要用,都不违法。

友情链接

PCIe扫盲——PCIe错误源详解(一)

2022.03.07 - TLP 是什么?

,又名 ECRC。

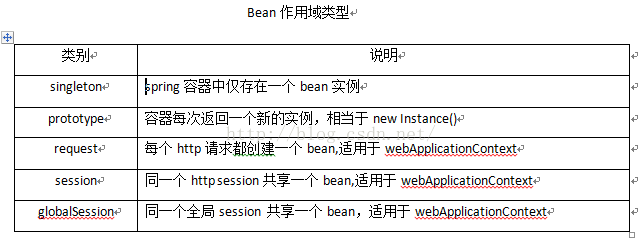

TLP 包格式: + + Data + 。TLP 便是这 TLP 包的组成部分,位于 TLP 末尾,长度 1DW,存放了该 TLP 的 ECRC 值。

TLP 四大组成中,除了 ,其他都是可选项,包括 。TLP 中有一个字段 TD (TLP ),用以标记该 TLP 是否使用 ,或者说该 TLP 是否使用 ECRC。如果 显示该 TLP 不含 ,但最后收到了 ,这个 TLP 就是个畸形包,要上报错误。

▲ 图1 TLP 包格式

2022.03.08 - EP 和 EP 是啥?

EP 分两种: EP 及 EP。 EP 是指原本给 PCI-X 总线接口设计的 EP 被改为 PCIe 总线接口 EP。 EP 是指标准的 PCIe EP。 EP 支持部分 EP 禁止的操作, EP 全部通过内存映射来操作。两者比较如 表1 所示。

▼ 表1 EP Vs. EP

2022.03.09 - PCIe LCRC 和 ECRC 有何区别?

PCIe 采用 CRC 校验来检测 TLP 是否存在错误,根据检测层次不同可分为 LCRC 及 ECRC。

两者存在以下区别:

▼ 表1 LCRC Vs. ECRC

参考:

PCIe扫盲——PCIe错误检测机制

ECRC VS LCRC

2022.03.10 - PCIe 是什么?有什么用处?

DL 层在发生 TLP 前会给每一个 TLP 添加一个序列号,即 。

接收端 DL 层在检查完 LCRC 后对 进行检查,判断接收到的序列号是否与期望值一致,以此判断是否有丢包。出现丢包的话,依据 发送 NAK 请求重传丢掉的包。短时间内收到 相同的重复包不视为错误处理。

2022.03.11 - 是如何路由的?

路由方式有三种,以隐式路由为主,但也支持基于地址或 ID 的路由。TLP 中 Type 字段()指定了该 的路由方式,如表1。

▼ 表1 路由

对于与 RC 之间通信的 ,RC 为 的发起者或接收者,没必要指定地址和ID,采用隐式路由。目前除了 的 ,还没有基于地址进行路由的 类型。

参考

PCI Base Spec 5.0, 2.

老男孩读PCIe之七:TLP的路由

PCIe系列第四讲、TLP的路由方式

2022.03.12 - 收到不支持的 是如何处理的?

回复 UR。不支持的 是指 Code 未识别。

2022.03.13 - LTSSM EQ ~ 都在干啥?

PCIe LTSSM 链路均衡,即 EQ (),是 LTSSM 的一个子状态。PCIe 在首次进入 8 GT/s及以上速率时要进行 EQ,调整收发端电气参数以改善信号质量,满足高速信号传输的信号质量需求。

EQ 有 ~ 四个阶段。TS1 或 TS2 6 中包含 EC 字段来指示当前处于 EQ 的哪个 phase。各 Phase 工作内容如下:

EQ :EC=0。USP 回传 及 给 DSP。DSP 没有 。

EQ :EC=1。DSP 及 USP 发送其 LF (Low ,)、FS (Full Swing,) 、Post- () 给对端 ,在 /3 使用。

EQ :EC=2。USP 作为 ,调节 DSP 的 Tx 系数。具体可分为 调节及 调节。

EQ :EC=3。DSP 作为 ,调节 USP 的 Tx 系数。同 。

以上四个 phase 中,/1 采用 粗调,/3 精调。如果粗调阶段就达到了信号质量需求,也可以不进行精调。

除非有特别配置,8 GT/s 以上速率时必须进行 EQ,至少在最高速率上要进行 EQ,中间速率可以跳过 EQ。当然仿真的时候可以设置 ,或者设置 _rate,仅在最高速率时进行 EQ。比如最高支持 32 GT/s,那么在 8 GT/s,16 GT/s 的时候可以跳过 EQ。从 32GT/s 降速时,需要重新进行 并EQ。

参考

PCI Base Spec 5.0, 4.2.3

PCI 学习篇—物理层LTSSM(三) .详解

2022.03.14 - PCIe 地址空间有哪几种访问模式?DBI、ELBI、LBC、CDM 是啥?

PCIe 寄存器访问支持 Wire 和 DBI 两种模式。Wire 是对端 PCIe 访问本地寄存器(CDM 内部寄存器或 ELBI 外部应用寄存器)。DBI 是本地 CPU 等 访问本地寄存器。几个概念介绍如下:

DBI,Data Bus ,EP 侧的 CPU 可以通过 DBI 接口 PCIe 的 CDM 内部寄存器,也可以访问 ELBI 外部应用寄存器。

ELBI, Local Bus ,把 PCIe 收到的 寄存器读写请求转发到外部应用寄存器。

CDM,- ,含标准的 PCIe 配置空间及 PCIe 指定的寄存器空间(端口逻辑寄存器)。

LBC,Local Bus ,EP 的 LBC 给对端 USP 或本地 CPU 提供一种通过 DBI 访问 CDM 内部寄存器及 ELBI 外部应用寄存器的机制。

参考

book, 3.5

PCIE协议解析 IP DBI and LBC 读书笔记

2022.03.15 - PCIe 热切换和热插拔是什么?

PCIe 热切换和热插拔是一种在不关闭系统电源情况下更换 PCIe 卡设备的技术,能够确保换卡的同时 PCIe 系统持续不间断的运行。热插拔适用于 PC 及服务器主板上的 PCIe 板卡链接,热切换适用于 PCI。

PCIe 卡有两个为热插拔而设计的引脚——PRSNT#1 和 PRSNT#2,这两个引脚位于金手指两侧,比其他引脚要短。当 PCIe 板卡被拔出时,这两个引脚能够先于其他引脚检测到板卡正在被拔出。在这两个引脚检测到 PCIe 卡拔出、其他引脚断开连接之前这段时间内,系统软件协同主板热插拔驱动器、PCIe 卡设备驱动以及 PCIe 卡硬件进行热插拔处理,有序切断电源。

参考

PCI Base Spec 5.0, 6.7

PCI、PCI-X 和 PCI 的原理及体系结构,马鸣锦

PCIe扫盲——热插拔简要介绍

2022.03.16 - MSI 和 MSI-X 是什么?

MSI 和 MSI-X 都是消息信号中断。它们虽然叫 ,但它们不是 ,而是带有 1DW 数据载荷的一笔存储器写事务。

MSI 能力结构中定义了消息地址(即接收中断的存储器地址,32bit 或 64bit)、消息数据等,不同的消息数据代表不同的中断。MSI 最多支持 32 个中断,这 32 个中断对应唯一的地址。

随着系统的发展,单一消息地址及最高 32 个中断的现状无法满足需求。MSI-X 对 MSI 做了扩展,最多支持 2048 个中断,且每个中断可以对应不同的地址。为了实现以上功能,MSI-X 能力结构中不再指定单一的消息地址,而是替换为 MSI-X 表地址,这个表中每一个 Entry 对应控制一条中断。

友情链接

PCIe扫盲——中断机制介绍(MSI)

PCIe扫盲——中断机制介绍(MSI-X)

2022.03.17 - PCIe 采用了哪些主要的信号补偿技术?

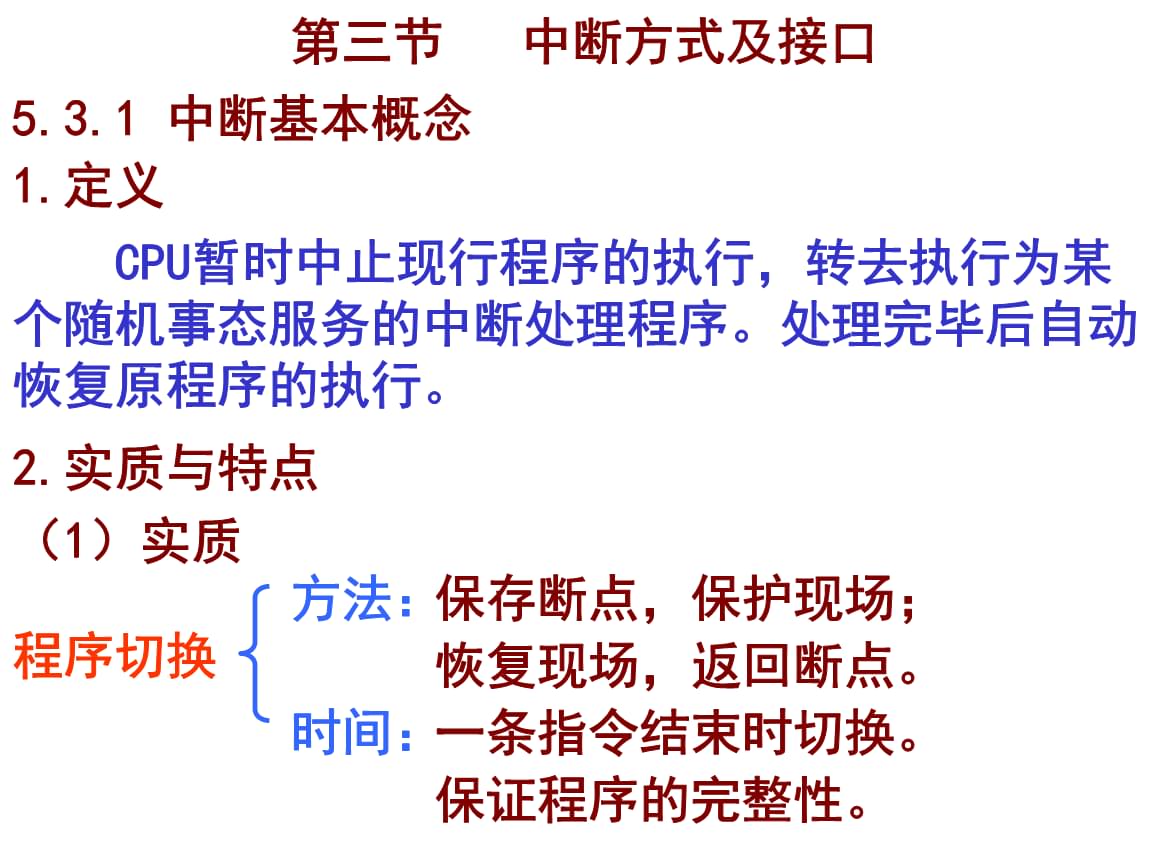

信号补偿三大技术:发送端预加重(Pre-)、去加重(De-)和接收端均衡()。预加重、去加重也被称为发送端均衡。各技术基本原理如图 1 所示。

▲ 图1 预加重、去加重、接收端均衡原理

无源传输线路像是一个低通滤波器,PCIe 高速串行信号经信道从发送端传输到接收端后,其高频分量比低频分量衰减要大,而高频分量主要集中在信号的上升沿及下降沿。为了补偿这种高频衰减,在信号发送的时候,有意增强信号跳变沿的信号幅度,增高高频分量,即信号预加重;相比于预加重的方案,去加重则是降低跳变沿之外的信号幅度,削弱低频分量,同样能够达到目的。

接收端均衡器相当于高通滤波器,来补偿失真的波形。

友情链接

信号完整性测试两大法宝–加重与均衡

PCIe扫盲——物理层电气部分基础(二)之De-

2022.03.18 - . 中两端的 1024 个 TS 有什么发送顺序吗?

没有顺序要求。

假设 Bit = 0, = PAD, = PAD 。

完成之后 Tx/Rx 进入 . 状态,任一端确保其 Tx 部分稳定后即可发送 TS1,没有先后顺序要求,具体取决于退出 的时刻。两端 Rx 依据其收到的 TS1 进行位锁定和符号锁定。任一端所有有效 Lane 上发送完 1024 TS1 且收到 8 TS1/TS2 后进入 .,改发 TS2。

以相连的 A、B 两个 PCIe 设备为例,重点说下为什么收到 8 TS1 或 8 TS2 :A 发完 1024 TS1 收到 8 TS1 后进 .,A 开始发 TS2;A 开始发 TS2 了,B 还处于 .,这时候 B 有可能还没完成锁定,那么 B 一个 TS1 都收不到。等完成锁定,收到的已经是 A 发来的 TS2 了。所以收到 8 TS2 也可以进 .

2022.03.19 - 本地 Rx 回环的时候恰好碰到对端 Tx 发送 TS1 怎么办,是有什么仲裁机制吗?

如果仅指单个 PCIe 设备 PHY 的 ,其进入 模式后,不再接收对端 Tx 发送的 TS1 (通过 Mux 实现)。

如果是两个 PCIe 设备间的 ,两者进入 是经过了协商的( 发 =1 的 TS1,Slave 回相同的 TS1),否则不会开始 BIST 测试。即不存在问题所述情况。

2022.03.20 - PCIe 有哪几种 模式?

PCIe 有三种 模式:

Local (PIPE),单个 PCIe 仅需 即可完成,没有 PHY 的参与。

Local ,单个 PCIe 即可完成,需要 ,过了 PHY。

,需要 和 Slave 两个 PCIe 完成,两端的 及 PHY 都需参与。

各种模式示意图如图 1 所示。

没有一种模式叫 ,想想为啥

2022.03.21 - 将 PCIe 从 L2 低功耗状态唤醒有哪几种方式?

有两种方式将 PCIe 从 L2 低功耗状态唤醒:

WAKE#,是一种 Side-band 信号。

, 是一种 30 kHz ~ 500 MHz 的低频 In-band 信号。在 L2 状态时,主电源及时钟都没有,但 电路使用的 Aux 电源仍然保留。UPS 发送 ,DSP 接收 ,方向不能反。DSP 检测到 后退回到 。

2022.03.22 - PCIe 是如何判断链路处于电气闲的?

PCIe 设备有两种方式来获知当前链路是否处于电气闲状态:

直接检测:模拟电路直接检测电路是否电气闲。

间接推测:依据收到的进行推测链路是否处于电气闲。

模拟电路直接检测的方法不必多说。出现以下情况时,PCIe 设备可推测链路处于电气闲。

L0 状态下,128 us 时间窗内 未检测到流控 DLLP 更新 和/或 未检测到 SKP。

. 状态下, Slave 在 128 us 内未检测到退出电气闲(仅 Gen1)。

. 状态下,1280 UI 时间内未检测到 TS1/2 @Gen1/Gen2,4 ms 时间内未检测到 TS1/2 @Gen3+。

.Speed 状态下,若上次速率协商成功,1280 UI 时间内未检测到 TS1/2 @Gen1/Gen2,4680 UI 时间内未检测到 TS1/2 @Gen3+。

.Speed 状态下,若上次速率协商失败,2000 UI 时间内未检测到 TS1/2 @Gen1,16000 UI 时间内未检测到 TS1/2 @Gen2+。

若此前已经处于电气闲,不可依据推测结果判断是否已经退出电气闲。在具体实现时,为了节省面积,往往在 LTSSM 中统一设置一个 来进行推测,而非每条 Lane 单独设置一个 。

2022.03.23 - 如何知道 TLP 的长度?

每个 TLP 固定长度 1DW,其中第 1Byte 是 Fmt 及 Type,用以指明当前为 TLP 。 1 个 TLP 不够可以继续追加,第二个 TLP 的第 1Byte 再来一次 Fmt 及 Type。

虽然TLP 中有 Fmt 及 Type,但那是 TLP 的,正式 TLP 中仍然需要 Fmt 及 Type。

2022.03.24 - EP 如何知道自己的 PASID 值是多少?软件是如何通知 EP PASID 值的?

PASID 是 EP 的本地 ID,由 EP 侧的系统软件进行分配,一般是把进程号用作 PASID。理论上 EP 每个 分到的 PASID 都应该是正交的,但实际上大家似乎没有遵守这个规则。至于软件是如何通知 EP PASID 值的,PCIe Spec 没有明确指出,应该是系统软件写 PCIe 中的相关寄存器吧,厂商自行实现。

2022.03.25 - PCIe 加扰解扰时,什么情况下会初始化 LFSR ?

Gen1/Gen2 时,COM 符号初始化 LFSR 为 FFFFh。

Gen3 及以上时,发送/接收完 EIEOS 最后一个 初始化 LFSR,[2:0] 不同初始值也不同。

2022.03.26 - PCIe 有序集什么时候加扰,什么时候不加扰?

Gen1/Gen2 时,K 码不加扰,除 OS 外的 D 码、 、 都需要加扰。为了便于调试,也可以通过 TS sym5 bit3 软件控制关闭加扰功能。

Gen3 及以上时,对于 TS1 及 TS2,Sym0 无需加解扰,Sym1~Sym13 需要加解扰,Sym14~Sym15 根据需要可加解扰可不加解扰,为了 DC 可以不加解扰。

FTSOS、SDS、EIEOS、EIOS、SKPOS 不加解扰。除 SKPOS 外,其他 OS 即便不加解扰,LFSR 也照常推进。

2022.03.27 - PCIe TS1/TS2 是如何实现 DC 的?

对于 Gen1/Gen2 ,8b/10b 编码自带 DC 功能。

对于 Gen3 及以上,128b/130b 只在 前添加 2bit 同步头,不具备8b/10b那样的 DC 能力,依靠加扰来实现一定程度的 DC 。TS1 或 TS2 的 16 个 中,Sym0 无需加扰,Sym1~Sym13 需要加扰,Sym14~Sym15 根据 DC 的需要可加扰可不加扰。

为了采用 Sym14、Sym15 实现 DC ,每条 Tx Lane 都有一个独立的模块监测其已发送的 bit1 和 bit0 的数量差。当差值达到 511 之后不再继续加,但是可以减少。具体规则如下:

如果发完 Sym11 后差值 >31,Sym14、Sym15 均不加扰,均用作 DC 。若 1 比 0 多,则多发点 0, Sym14 发送 20h(),Sym15 发送 08h();若 0 比 1 多,则多发点 1, Sym14 发送 DFh(),Sym15 发送 F7h()。

如果发完 Sym11 后差值 >15,Sym14 加扰照常发送 TS 标识符,Sym15 不加扰用作 DC 。若 1 比 0 多,则多发点 0,Sym15 发送 08h();若 0 比 1 多,则多发点 1,Sym15 发送 F7h()。

如果发完 Sym11 后差值 Gen3 做一次 EQ 进行第一次调速,进入 EQ 后 清零 。

第二次切速进入 . 后收到的 TS 中才切为最大支持 16 GT/s,符合规则 (iii), 置一,Gen3 -> Gen4 做一次 EQ 进行第二次调速,进入 EQ 后 清零 。

也就是说,切速过程为 Gen1 -> Gen3 -> Gen4,每次切速都做一次 EQ。

2022.03.30 - 我 Gen4 速率开启了 to rate,为什么没起作用?

当最高速率为 Gen5 且开启了 to rate 时,只进行一次切速/EQ,即 Gen1 -> Gen5。 to rate 是 Gen5 的 ,若目标速率为 Gen3/Gen4 且开启了 to rate,不是像 Gen5 那样只在最高速率进行一次 EQ,而是不进行 EQ,直接从 Gen1 -> Gen3/4,没有中间速度。用 VIP 进行仿真时, VIP会报错。

2022.03.31 - RC 和 EP 如何知道它们中间有 ?

TS2 5 有两个 field 来指示是否有 ,TS2 经过 时, 会更改这两个字段。

bit4 为 Bit,仅在 2.5 GT/s 速率时有效,该位为 1 时表示 RC-EP 间至少有一个 。

bit5 为 Two Bit,仅在 2.5 GT/s 速率时有效,该位为 1 时表示 RC-EP 间至少有两个 。对于 16 GT/s 及以上速率,必须实现该 field,对 8 GT/s 可选。