verilog时钟问题

1.时钟IP核分频也有精度,当输入时钟和输出时钟频率不是整数倍的时候,可能会有误差。如:用时钟IP核,输入时钟是50MHz,输出时钟是25.6MHz,输出频率的周期会有0.001ns的误差,但是误差极小,不影响使用

2.仿真精度最大到0.001ns

3.时钟IP核可以分出MHz的信号,小频率的用计数器分,当不是整数倍的时候会有误差

4.ROM IP核给的时钟是系统时钟,IP核把这个当作基准时钟,换其他时钟也可以

5.一个工程里的块尽量用同一个时钟来驱动,一个系统里基本保持一个统一的系统时钟 这样不会跨时钟域,否则可能出现时序问题。其他地方可以用使能时钟触发

6.不能使用同一个时钟的上升沿和下降沿同时驱动块,如:@( or )

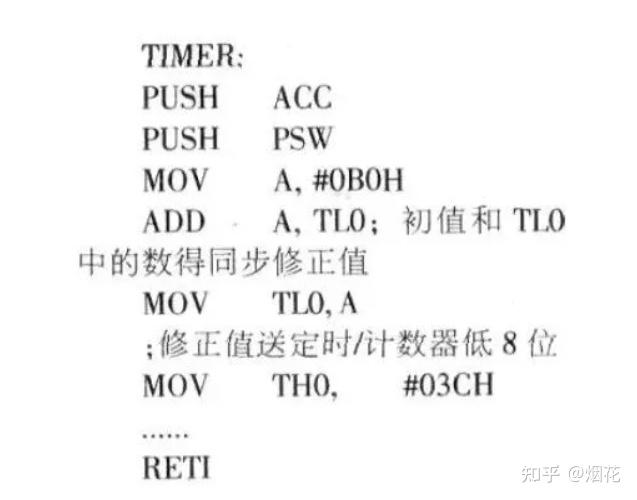

7.禁止用计数器分频后的信号做其它模块的时钟,而要用改成时钟使能的方式,否则这种时钟满天飞的方式对设计的可靠性极为不利,也大大增加了静态时序分析的复杂性

时钟使能

`timescale 1ns / 1psmodule bit(input rst ,input rc_clk ,output bit

);

reg [6:0] cnt;

always@(posedge rc_clk)beginif(rst) cnt<=7'b0;else if(cnt==7'd126) cnt<=7'b0;else cnt<=cnt+1'b1;

end always@(posedge rc_clk)beginif(rst) bit_clk<=0;else if(cnt==0) bit_clk<=1'b1;else if(cnt==7'd1) bit_clk<=1'b0;else bit_clk<=bit_clk;

end bit_rom u_bit_rom(.clka(bit_clk), // input wire clka.ena(1'b1), // input wire ena.addra(addra), // input wire [7 : 0] addra.douta(bit) // output wire [0 : 0] douta

); reg [7:0] addra;

always@(posedge rc_clk)beginif(rst)addra<=8'b0;else if(bit_clk)addra<=addra+1'b1;else addra<=addra;

end reg [7:0] addra1;

always@(posedge bit_clk)beginif(rst)addra1<=0;elseaddra1<=addra1+1'b1;

end endmodule