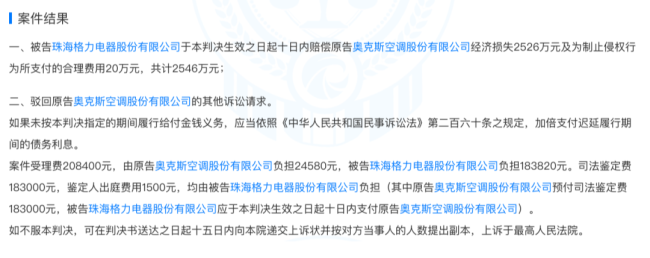

mask是什么意思?什么是4Mask、5Mask、6Mask、8Mask工艺

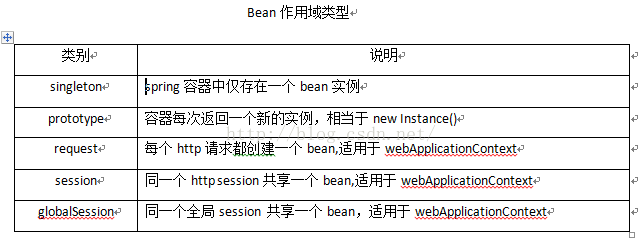

掩膜是什么意思(什么是4Mask、5Mask、6Mask、8Mask工艺) 目前非晶硅阵列基板常用5Mask或4Mask工艺,IGZ0金属氧化物阵列基板常用5Mask、6Mask或8Mask工艺。

如图1所示,非晶硅或IGZO阵列基板的5Mask工艺主要用于TN和VA模式。具体步骤包括:

第一道光刻工艺:形成栅电极图案,主要用作扫描线走线、面板外围走线、端子金属和一些打标图案(打标图案用于下道工序的对位参考);

第二光刻工艺:形成半导体图形,即非晶硅岛(或IGZ0半导体层),作为TFT沟道;

第三道光刻工艺:形成源漏金属层,主要包括数据线和TFT源漏电极;

第四道光刻工艺:形成接触孔,主要在TFT漏极、跳线和端子区;

第五道光刻工艺:形成ITO电极,主要用作像素电极、端面电极、跳线连接。

以上五款口罩都比较成熟,良品率也比较稳定。

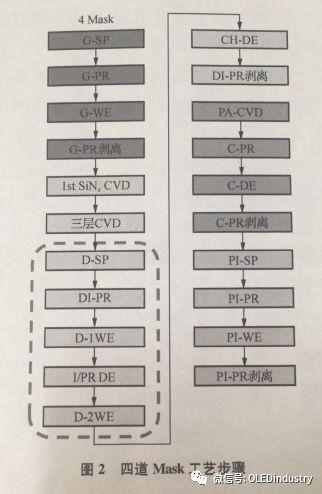

如图2所示,非晶硅或IGZO阵列基板的4Mask工艺主要用于TN和VA模式。与5Mask工艺不同的是,4Mask工艺对半导体层和源漏金属层使用相同的掩模,但这种掩模与普通掩模的不同之处在于它可以对不同位置的光刻胶施加不同程度的曝光。这种蒙版有两种,一种是半色调蒙版(Half-Tone Mask),另一种是灰度色调蒙版(Mask)。

4Mask与5Mask光刻工艺不同的步骤如下:

步骤一:连续沉积非晶硅半导体层(或IGZO半导体层)和源漏金属层。非晶硅层通过CVD沉积(IGZO半导体层通过CVD形成),金属层通过PVD形成。

第 2 步:涂上光刻胶。

第三步:对不需要金属的区域的源漏金属区域的光刻胶进行曝光(不同曝光量)、显影和刻蚀。金属是湿法蚀刻,而非晶硅是干法蚀刻(IGZO 半导体层是湿法蚀刻)。

第四步:灰化光刻胶,在沟道区暴露金风,然后进行金属湿法刻蚀和n﹢Si干法刻蚀,剥离光刻胶。

与5Mask相比,4Mask主要少了一张掩模版生产和相应的光刻胶涂布、曝光机显影工艺,从而节省了生产成本。

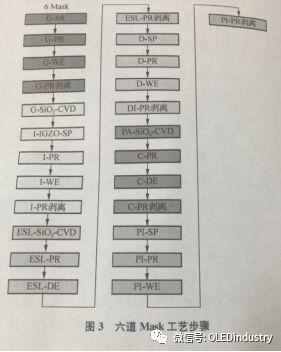

如图3所示,IGZO阵列基板的6Mask工艺主要用于VA模式。具体步骤包括:

第一道光刻工艺:形成栅电极图案,主要用作扫描线走线、面板外围走线、端子金属和一些打标图案(打标图案用于下道工序的对位参考);

第二光刻工艺:形成半导体图案,即IGZO半导体层,作为TFT沟道;

第三道光刻工艺:形成刻蚀阻挡层图案,以防止在湿法刻蚀源漏电极时对TFT沟道的IGZO层造成损伤;

第四道光刻工艺:形成源漏金属层,主要包括数据线和TFT源漏电极;

第五道光刻工艺:形成接触孔,主要在TFT漏极、跳线和端子区;

第六道光刻工艺:形成像素ITO电极,主要用作像素电极、端面电极、跳线连接。

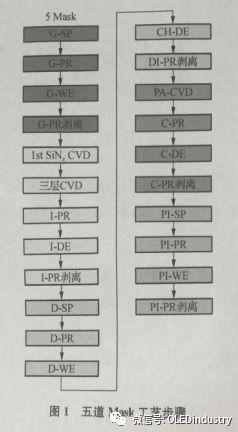

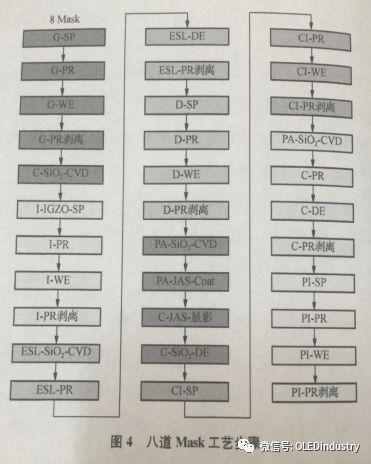

如图4所示,IGZO阵列基板的8Mask工艺主要用于FFS模式。具体步骤包括:

第一道光刻工艺:形成栅电极图案,主要用作扫描线走线、面板外围走线、端子金属和一些打标图案(打标图案用于下道工序的对位参考);

第二光刻工艺:形成半导体图案,即IGZO半导体层,作为TFT沟道;

第三道光刻工艺:形成刻蚀阻挡层图案,以防止在湿法刻蚀源漏电极时对TFT沟道的IGZO层造成损伤;

第四道光刻工艺:形成源漏金属层,主要包括数据线和TFT源漏电极;

第五道光刻工艺:形成第一接触孔,主要存在于TFT极、跳线和端子区;

第六道光刻工艺:形成COM-ITO电极,主要用作连接COM电极的跳线等;

第七道光刻工艺:形成第二接触孔,主要存在于TFT极、跳线和端子区;

第八道光刻工艺:形成像素ITO电极,主要用作像素电极、端面电极、跳线连接。

▼

郑重声明:本文版权归原作者所有,转载文章仅出于传播更多信息之目的。如作者信息标注有误,请尽快联系我们修改或删除,谢谢。