计算机组成原理--运算方法:加减乘除

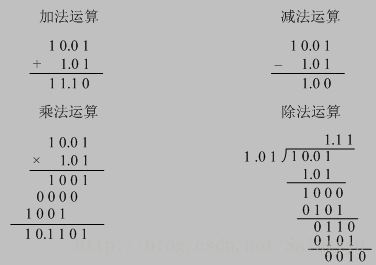

补码加减法

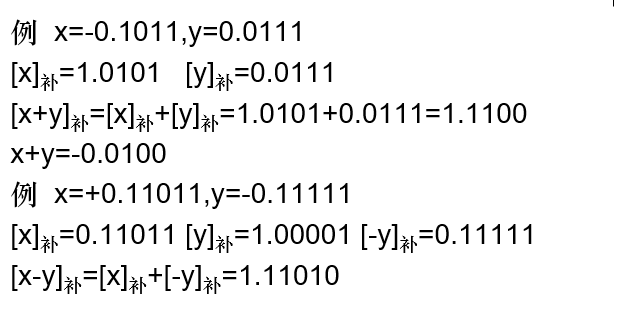

补码加法

公式:[x+y]补=[x]补+[y]补

补码减法:

为了将减法转变为加法,需证明公式: [x-y]补=[x]补+[-y]补 (证明)

为了求得同时[-y]补,需要证明[-y]补=[y]补+2^-n(意义是[-y]补等于[y]补取反,末位加1)

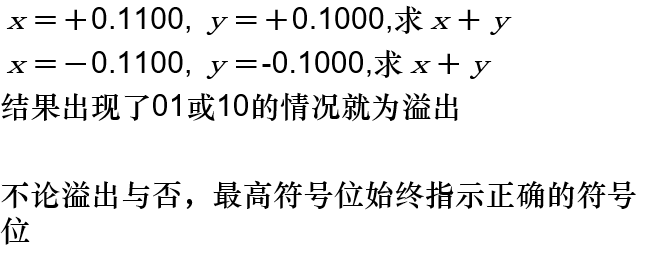

溢出检测

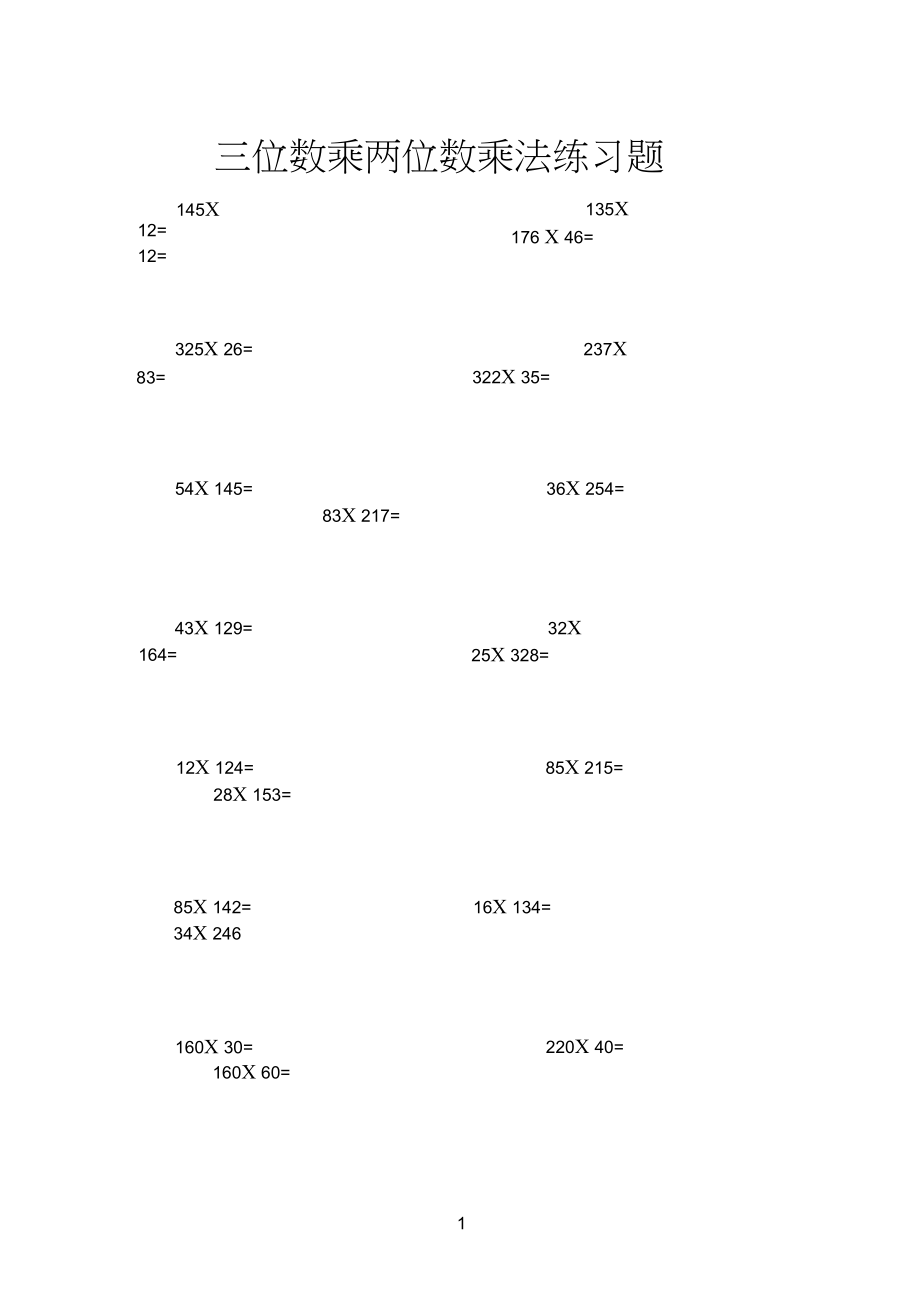

定点原码乘法 定点乘法原理

n位乘n位积可能为2n位.

乘积的最后是所有部分积之和,有n个数相加,而FA只有两个输入端,机器一次只能进行两个数的相加,不能进行多个数据的加法。

手工计算中,乘数的每一位是0还是1都可直接看见,而在计算机中,采用放乘数的寄存器的每一位直接决定本次相加数是被乘数还是0是很不方便的,若采用该寄存器的最低一位来执行这种判断就简便了。

计算机中执行乘法时,积的符号位由被乘数和乘数的符号位通过一个半加器(即异或门)实现。

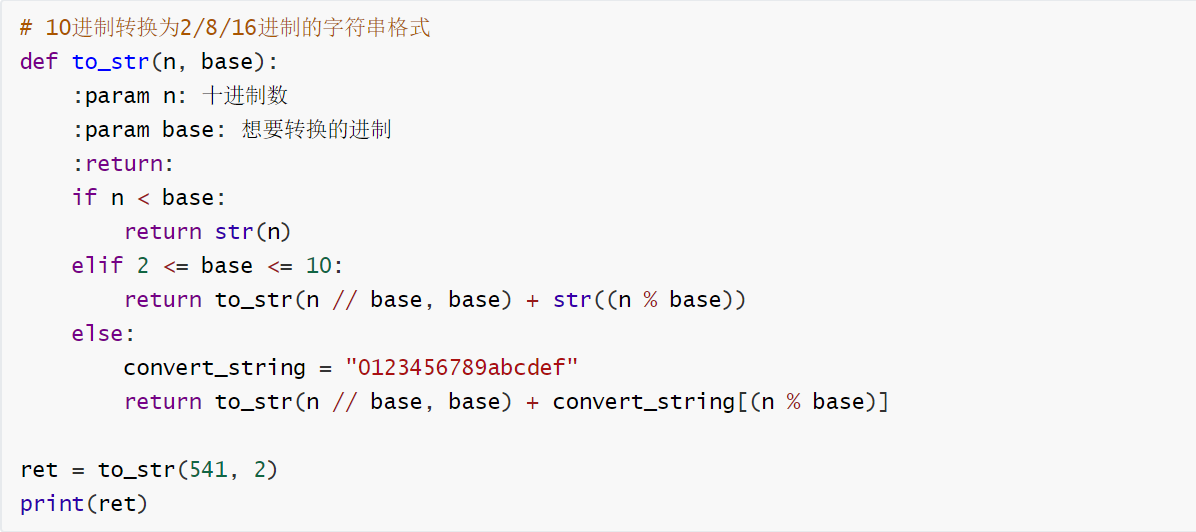

数值部分的运算规则是:从最低位Y0开始,当乘数Yi为1时,将上次部分积加上被乘数的绝对值,然后右移一位,得到新的部分积;当Yi为0时,则写下全0。然后再对乘数Y的高一位进行类似乘法运算。重复“加—右移”操作N次,可得到最后的乘积。

R0存放部分积,R2存放被乘数,R1存放乘数

R0清零,R2存放被乘数,R1存放乘数。乘法开始时,“启动”信号时控制CX置1,于是开启时序脉冲T,当乘数寄存器R1最末位为“1“时,部分积Z和被乘数X在加法器中相加,其结果输出至R0的输入端。一旦控制脉冲T到来,控制信号LDR0使部分积右移1位,与此同时,乘数寄存其R1也在控制信号LDR1作用下右移一位,且计数器I记数一次;

将步骤三重复执行N次

当计数器I=n时,计数器I的溢出信号使控制触法器CX置0,关闭时序脉冲T,乘法宣告结束

原码算法存在的缺点:

一是符号位需要单独运算,最后给运算结构以正确的符号;

二是对于采用补码存储的机器,从存储器中取出的是操作数的补码,需先将其转换成原码,这样很不方便,而且影响速度。

定点补码乘法

补码乘法的特点是乘数、被乘数用补码表示,符号位参加运算,希望得到的结果就是乘积的补码,符号位在运算中形成

定点补码乘法原理

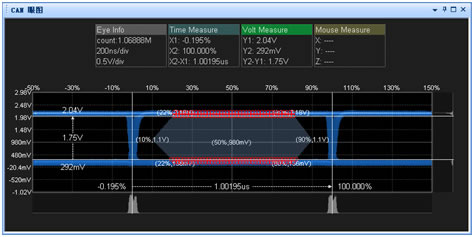

定点除法

在定点计算机中,完成两个原码表示的数相除时,商的符号由两数的符号位和原码乘法运算方法一样,用模2求和得到,而商的数值部分则是两个正数相除得到

计算机中执行除法时,商的符号位由被除数和除数的符号位通过一个半加器实现;

对于数值部分,由于定点小数的绝对值小于1,如果被除数大于或等于除数,则商就大于或等于1,因而会产生溢出,这是不允许的。

因此在执行除法以前,先要判别是否溢出,不溢出时才执行除法运算。判别溢出的方法是被除数减去除数,若差为正,就表示溢出,即要求被除数