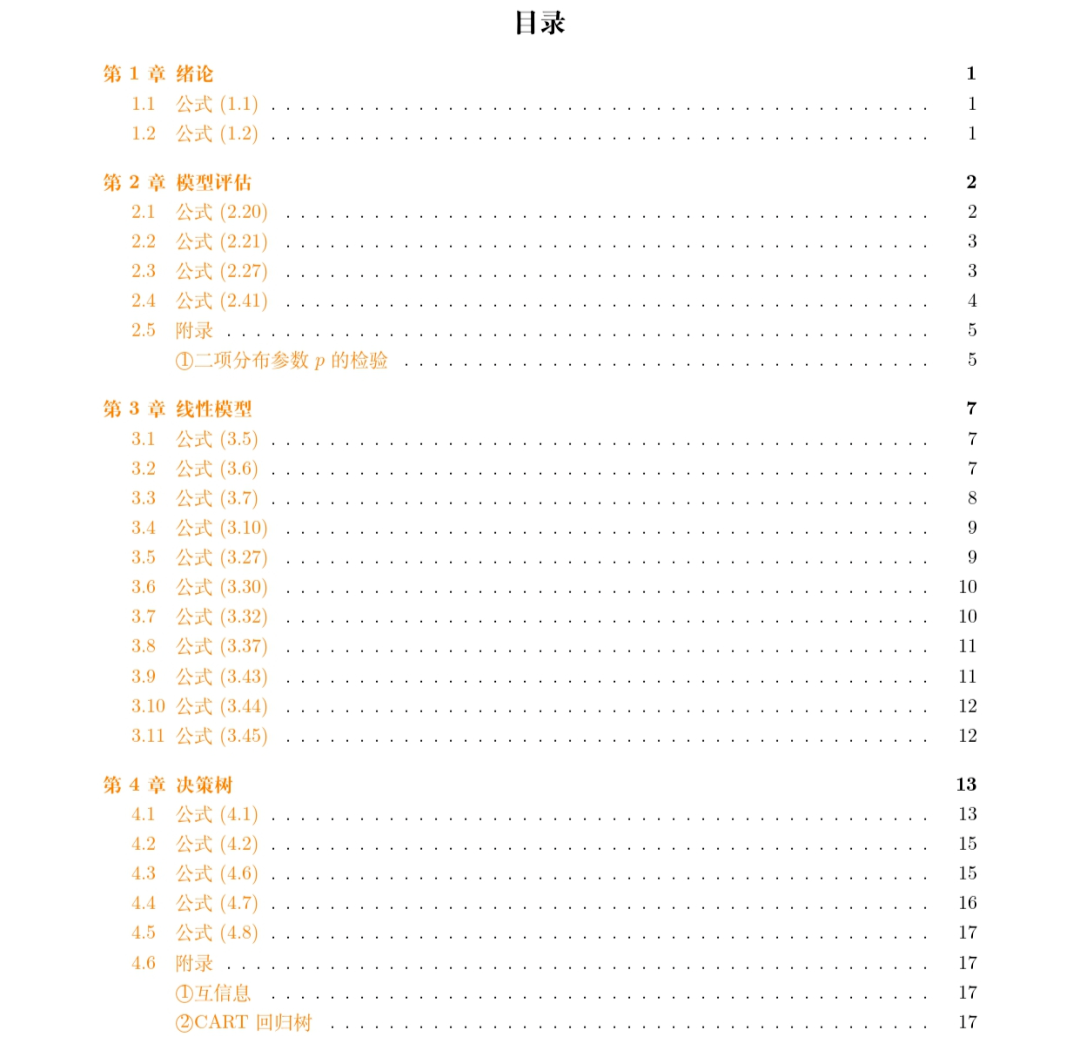

1.8 晶振 CRY Crystal

1.8 晶振 CRY

1 晶振是什么?

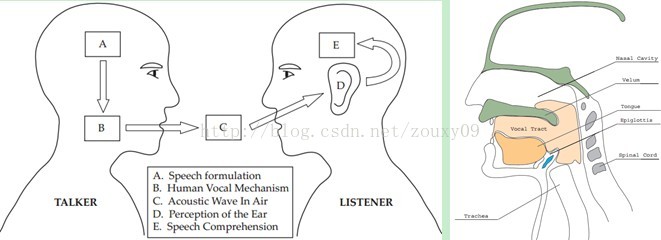

晶振:指的是石英晶体谐振器( unit)和石英晶体振荡器( )的统称。

无源晶振就是石英晶体谐振器的别称,英文名(),主要用在各种电子线路中起产生频率的作用.无源晶振一般是有2个引脚(有些不止2个引脚)的无极性元件,需要借助于时钟电路才能产生振荡信号,自身无法振荡起来,无源晶振分为直插式与贴片式. 无源晶振与有源晶振的英文名称不同,无源晶振(一般也叫无源晶体)为(晶体),而有源晶振则叫做(振荡器)。有源晶振有4只引脚,是一个完整的振荡器,其中除了石英晶体外,还有晶体管和阻容元件,因此体积较大。

无源晶振需要用DSP片内的振荡器,在上有建议的连接方法。无源晶振没有电压的问题,信号电平是可变的,也就是说是根据起振电路来决定的,同样的晶振可以适用于多种电压,可用于多种不同时钟信号电压要求的DSP,而且价格通常也较低,因此对于一般的应用如果条件许可建议用晶体,这尤其适合于产品线丰富批量大的生产者。无源晶体相对于有源晶振而言其缺陷是信号质量较差,通常需要精确匹配外围电路(用于信号匹配的电容、电感、电阻等),更换不同频率的晶体时周边配置电路需要做相应的调整。使用时建议采用精度较高的石英晶体,尽可能不要采用精度低的陶瓷晶体。

有源晶振是一个完整的振荡器,里面除了石英晶体外,还有晶体管和阻容元件。有源晶振不需要DSP的内部振荡器,信号质量好,比较稳定,而且连接方式相对简单(主要是做好电源滤波,通常使用一个电容和电感构成的PI型滤波网络,输出端用一个小阻值的电阻过滤信号即可),不需要复杂的配置电路。相对于无源晶体,有源晶振的缺陷是其信号电平是固定的,需要选择好合适输出电平,灵活性较差,价格相对较高。对于时序要求敏感的应用,还是有源的晶振好,因此可以选用比较精密的晶振,甚至是高档的温度补偿晶振。有些DSP内部没有起振电路,只能使用有源的晶振,如TI的6000系列等。有源晶振相比于无源晶体通常体积较大,许多有源晶振是表贴的,体积和晶体相当,有的甚至比许多晶体还要小。

有源晶振用途

有源晶振型号众多,而且每一种型号的引脚定义都有所不同,接法也不同,下面我介绍一下有源晶振引脚识别,以方便大家:有个点标记的为1脚,按逆时针(管脚向下)分别为2、3、4。通常的用法:一脚悬空,二脚接地,三脚接输出,四脚接电压。

有源晶振是用石英晶体组成的,石英晶片之所以能当为振荡器使用,是基于它的压电效应:在晶片的两个极上加一电场,会使晶体产生机械变形;在石英晶片上加上交变电压,晶体就会产生机械振动,同时机械变形振动又会产生交变电场,虽然这种交变电场的电压极其微弱,但其振动频率是十分稳定的。当外加交变电压的频率与晶片的固有频率(由晶片的尺寸和形状决定)相等时,机械振动的幅度将急剧增加,这种现象称为“压电谐振”。

压电谐振状态的建立和维持都必须借助于振荡器电路才能实现。

从PC诞生,主板上一直都使用一颗14.的石英晶体振荡器作为基准频率源。主板上除了这颗14.的晶振,还能找到一颗频率为32.的晶振,它被用于实时时钟(RTC)电路中,显示精确的时间和日期.

实际数据

测试样品为的711SC 1.000M的输出频率,1脚悬空,2脚接地,3脚输出,4脚接+5V;

1.4V就开始起振,峰值电压1.64V,但是工作频率会有一定的偏差;3V时峰值电压3.24V,工作频率1.000M,输出频率准确;5V时峰值电压为5.6V,工作频率1.000M,输出频率准确。

2 怎么判断是无源晶体还是有源晶振?

封装上:

有源晶振的都是要有VCC供电引脚的,而无源晶体则没有.

从外观上:

二个脚的肯定是无源晶振,不是有源晶振。有源晶振至少3只脚(地/输出/电压),多数为4只脚,也有5只脚和6只脚的。4只脚的晶振可能是无源晶振(一般是2/4脚为地)也可能是有源晶振。

有源晶振会打原点标记1号引脚.

从规格书:

晶体的规格书上都是 或者 unit的字样

而有源晶振的规格书就会有 的字样

贴片晶振有一个脚位有一点缺口,这个脚即为1号脚,背面视图顺时针数;就可以清楚的分辨出脚1、2、3、4脚位,通常四脚无源晶振我们知道,只有两个脚是功能脚,其余两个脚起不到任何作用,电路中,脚1和脚3是通电的,电流从脚1流入、脚3流出。

无源晶振底面视图:底面视图中2号脚和4号脚都是GND,焊盘是连通的,和晶振的盖子也是连通的,在线路板上使有时接地和不接地都没有关系。这两个焊盘的主要作用是在贴片时更好的把晶振固定在线路板上。

总结:无源晶振无论是两脚还是四脚的都是没有方向的,两脚的不用说,怎么接都行;四脚的1,3为功能脚,2,4脚接地。通常1(XTAL1)接输入,3(XTAL2)接输出,因为没有极性的区分,晶振也都是长方体,所以就算旋转180度贴片,也就是1,3倒过来也是可以的。

也有见过下面这种标识的,缺脚的为4号脚,而且2跟4内部不是短接的,不知道是不是标错了,这种很少见。

3 等效模型是什么?

一个简单的晶体模型如图1所示。它具有R-L-C系列元件,称为运动电阻、运动电容和运动电感。并联电容器C0被称为并联电容,并对封装电容进行建模。图2展示了一个由反相放大器和晶体组成的简单振荡器模型及其等效电路模型。

图2中的电路模型有助于理解振荡的必要条件。这些是:

XXTAL + XOSC = 0;RXTAL + ROSC = 0

其中:

XXTAL=由晶体表示的阻抗的虚部。

RXTAL=由晶体表示的阻抗的实部。

XOSC=由振荡器表示的阻抗的虚部。

ROSC=由振荡器表示的阻抗的实部。

从数学上讲,ROSC是一个负电阻。它代表一种提供功率而不是耗散功率的电路,例如放大器。因此,一个简单的解释是,放大器必须有足够的增益来补偿晶体所代表的损耗。负电阻的概念对晶体振荡器的设计很重要,后面再详细讨论。

4 相关参数有哪些?

晶振规格书上通常有如下几个参数。(负载电容CL单独介绍)

晶体的振荡工作模式必须选择基本模式。一些晶体以泛音模式( mode)工作以实现更高的频率,通常在30MHz以上。这是因为随着频率的增加,在基本模式下操作所需的晶体尺寸减小,并且在制造过程中的某个时刻变得更加难以处理。因此,高频基模晶体更昂贵。

选择并联谐振模式下工作的晶振。

1. (初始偏差):频率公差是指在指定温度下,通常为25°C时,与标称晶体频率的初始最大偏差。该公差规范说明了晶体制造和组装中的正常变化。许多水晶供应商在订购水晶时提供固定的公差值选择。例如,可排序值的集合可以是+/-20 ppm、+/-50 ppm和+/-100 ppm。

2. (温度偏差):频率稳定性是指在特定温度范围内与标称晶体频率的最大偏差。该偏差是参考25°C下的标称频率进行测量的。晶体供应商在订购晶体时也可以提供一系列的值供选择。例如,在指定的温度范围内,常见的范围可能包括+/-50ppm和+/-。对于指定在-40摄氏度至+125摄氏度的温度范围内运行的汽车晶体,+/-50 ppm,每摄氏度的偏差为1.64 ppm。

3.Aging(长期稳定性):老化是指晶体经历的振荡频率随时间的累积变化。晶体老化的原因有很多,包括过度的驱动水平、各种热效应以及机械结构上的应力消除或积聚。老化通常以每年ppm为单位进行规定。长期稳定性的典型值可能在每年±3 ppm至±5 ppm之间。

4.Drive Level(耗散功率):晶体驱动电平表示由晶体耗散的功率。可接受的最大值将出现在晶体数据表上(一般都是最大值100uW)。超过晶体的最大驱动水平会导致性能下降并缩短晶体的使用寿命。建议在电路中插入一个串联电阻器RS,如图5所示。RS和CL2的组合成为分压器,使得晶体输入处的电压幅度减小。RS的起始值可以使用以下等式找到:

这个方程表示,RS必须设置为等于晶体谐振频率下CL2的阻抗大小,或者,RS=|ZCL2|。例如,如果CL2=16pF,在25MHz的晶体频率下,RS=398欧姆。 由公式Rc=1/(2πfC)=1/ωC=1/(23.^(-6))=398Ω。(常用330Ω来代替)

5. Rr:等效串联电阻(ESR)是晶体在串联谐振频率下表现出的电阻。ESR不能与晶体等效电路的运动电阻(RM)混淆。ESR与RM的关系式如下:ESR=RM*(1+C0/CL)^2

ESR通常被指定为以欧姆为单位的最大电阻值。ESR之所以重要,有两个原因:

1.与振荡器启动和维持振荡所需的环路增益成比例。

2.它与晶体中耗散的功率成比例,也称为驱动电平。

在上面等效模型中引入了负电阻的概念,并将其描述为振荡器必须提供的功率量,以补偿晶体中的损耗。其值由以下公式给出:

gM=用于形成放大器的MOS晶体管的小信号模型的跨导。ω=振荡器的谐振频率。CL1=CL2=上图的匹配电容。

一般经验法则是振荡器负电阻的大小必须≥5ESR,以确保电路启动并维持振荡。换句话说:|RNEG|≥5ESR。(后面测试章节也有提到,实测负阻大于10倍的ESR)

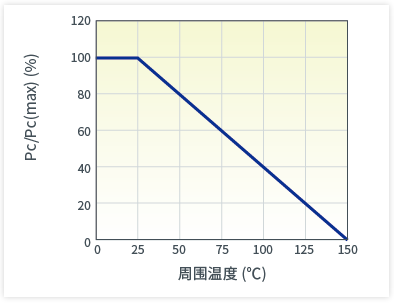

注意,RNEG与负载电容成反比。随着负载电容的增加,RNEG降低,即振荡器克服晶体损耗和达到稳定振荡的能力降低。图4中的图表说明了在125摄氏度和85摄氏度的温度下,TI的以太网PHY振荡器电路对应于负载电容范围的负电阻值。在同一张图上绘制了一组水平线,用5倍乘法器表示晶体ESR的各种值。对于任何给定的ESR值,其代表线和RNEG曲线之间的交点表示具有该ESR值的晶体的最大推荐负载电容。例如,如果预期的最坏情况操作温度为125摄氏度,则ESR为30欧姆的晶体必须使用不大于约25pf的负载电容。任何更高的负载电容都会导致负电阻降至建议的5倍容限以下。

考虑到汽车以太网需要+/-的总精度,必须选择晶体规格以满足该总精度。总精度是频率公差、稳定性、老化和器件公差(指负载电容)的总和,所有这些都在前面介绍。换句话说:准确度=频率公差+稳定性+老化+器件公差≤+/-100 ppm。

假设+/-100 ppm的要求涵盖-40摄氏度至+125摄氏度的温度范围,主机系统的预期使用寿命为5年,老化规格为每年3 ppm。假设由于器件公差造成的误差为8 ppm(后面章节提到的由于负载电容变化导致的误差)。然后可以重新排列精度方程,以确定公差和稳定性合起来的界限:100–8–(5x3)=+/-77 ppm,所以对于公差+稳定性预算为+/-77 ppm。例如,为了满足该预算,将选择公差为+/-20ppm且稳定性为+/-50ppm的晶体。

5 负载电容CL计算

晶振与匹配电容的总结

如下参考博通资料 mode.pdf

CL(Load )为晶体元件的负载电容是指在电路中跨接晶体两端的总的外界有效电容,包括外部匹配电容和杂散电容,是晶振要正常震荡所需要的电容。

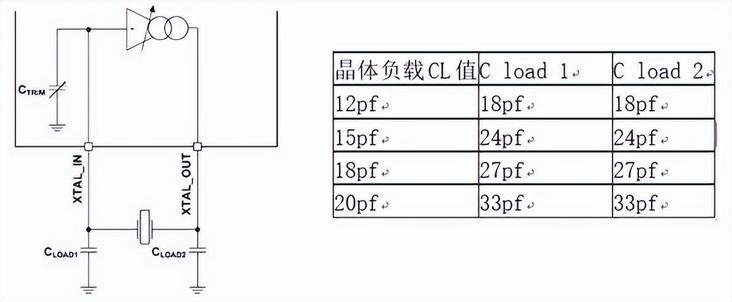

Cx1跟Cx2是晶振的匹配电容。

Cs为杂散电容(Stray ),也叫寄生电容。通常时2pF-5pF。

R1跟R2用于调节电路的Q值,所以这两个电阻预留上还是有必要的。

如下参考TI资料,考虑较为严谨,增加Cpin。

•CPIN是IC及其封装的XI和XO引脚的电容。大多数PHY规格书会给出该引脚电容。例如,-Q1对于每个引脚的XI和XO电容是1pF。

•是连接到晶体端子的印刷电路板(PCB)迹线的杂散电容。

•CL1和CL2是离散负载电容器。必须选择CL1和CL2,以使晶体电路看到的总负载电容接近晶体制造商指定的负载电容。

通常,CPIN+的范围从2pF到5pF,这取决于板布局设计。通过将晶体放置得尽可能靠近PHY的XI/XO引脚,从而实现短迹线,可以最小化杂散电容。

在大多数情况下,CL1=CL2。在这种情况下,CLOAD的方程式简化为:CLOAD=CL1/2+CPIN+

根据公式f=1/[2π√(LC)]可知,如果实际负载电容小于晶体规格规定的电容,晶体的振荡频率将增加。如果实际负载电容大于晶体规格规定的电容,晶体的振荡频率将降低。然而,与频率容限、稳定性和老化相比,负载电容的变化通常是振荡器频率的最小误差源。例如,对于指定的CLOAD=18pF、标称CL1=CL2=30pF、CPIN=1pF和=2pF,CLOAD的+/-10%变化(=CL1/2+CPIN+)将导致振荡器频率的偏差小于+/-8ppm。(这个8ppm是怎么算的呢?)

另外一种计算方式(更加详细严谨)

晶振负载电容外匹配电容计算与晶振振荡电路设计经验总结

如果从石英晶体插脚两端向振荡电路方向看进去的全部有效电容为该振荡电路加给石英晶体的负载电容。石英晶体的负载电容的定义如下式:

其中CS为晶体两个管脚之间的寄生电容(又名晶振静态电容或Shunt ),在晶体的规格书上可以找到具体值,一般0.2pF~8pF不等。晶振规格书上通常有一个C0即Shunt ,是晶振两个管脚之间的并联/寄生/静态电容,应该是属于Cs的一部分,通常近似Cs=C0。有时也取典型值=5pf。

CG指的是晶体振荡电路输入管脚到GND的总电容,其容值为以下三个部分的和。

● 外加晶振主芯片管脚芯到GND的寄生电容 CXI

● 晶体震荡电路PCB走线到到GND的寄生电容

● 电路上外增加的并联到GND的外匹配电容 CL1

CD指的是晶体振荡电路输出管脚到GND的总电容。容值为以下三个部分的和。

● 外加晶振主芯片管脚芯到GND的寄生电容 CXO

● 晶体震荡电路PCB走线到到GND的寄生电容

● 电路上外增加的并联到GND的外匹配电容CL2

TDA4最新版规格书有很多关于晶振电容参数的计算,这部分是一致的

TDA4规格书

这下面则是提到对晶振选型的时候还要注意它的并联电容Co,不能超过主芯片这端限定的最大值。这个并联电容包括晶振两个管脚之间的并联电容Co,两根PCB走线相互之间的电容,主芯片两个管脚之间的电容CXIXO。另外一个就是使走线尽可能短,相互之间不要靠太近来减小走线相互之间的电容,如果走线靠太近需要在他们之间添加地线来减小相互之间的电容。

这里举例按上面的截图要求当晶振为25M,ESR为30R时,并联电容最大为7pF。所以算出来晶振本身管脚的并联电容值Co不能超过6.95pF。

下面是另一个芯片的规格书上的描述,也是一样的计算方式。

考虑了内部CIN=CIN1=CIN2=12pF,所以CL1=CL2=2*12.5-12.5=12.5pF.(这里相当于忽略CPCB)

6 注意事项

1、晶振和负载电容尽量靠近芯片XI和XO引脚的位置,走线短且直。短迹线有助于减少寄生电感和杂散电容,并可以减少噪声耦合量。

2、避免在晶体或XI和XO迹线正下方布线任何其他信号迹线,尤其是它们不得与时钟迹线平行。使所有其他信号痕迹远离XI和XO痕迹。如果

应用需要在晶体下走线,则需要在晶体电路和其他信号走线之间使用接地平面。走线过程不能隔断,不要过孔换层。

3、尽量设计晶振位于远离电磁波干扰区域,如远离电源,天线等器件。

4、晶振电路下面的各层都需要铺地,不能放置器件和走线,尤其是高频信号线路;

5、屏蔽晶振,金属外壳检查接地。

6、请勿使用晶体输出驱动任何其他设备。晶体振荡器被设计为在直接反馈回路中驱动晶体。任何额外的分支或负载都可能影响振荡器的正常工作。

关于长度是否需要相等:

首先需要指出的是,只有无源晶振除了频率输出脚,还有另外一个频率输入脚。有源晶振没有频率输入脚,它的主要脚位包括电压输入脚与频率输出脚,因此这里所指的“晶振两端布线长度”为无源晶振,即石英晶体谐振器(),而非有源晶振(OSC)。

无源晶振两端(即频率输出脚与输入脚)布线长度尽量等同,并且尽量靠近IC管脚,特别是晶振频率越高时越要注意。同时建议,晶振本身也是噪声源,因此要求晶振PCB布线设计走线越短越好。

无源晶振频率信号输入端与其频率信号输出端布线长度等同的目的是保持晶振输出频率的稳定性,该原理等同于给晶振这两个管脚分别串联两颗同值电容的原因。比如,在晶振PCB布线设计时,基于晶振本身的负载电容值及PCB杂散电容对晶振的影响,一般情况下会给无源晶振32.的两个管脚分别串联一颗同值的15~18PF电容。换句话说,我们建议若晶振的频率输入脚串联的为15PF的电容,那么,该颗晶振的频率信号输出脚位串联的电容值也应该为15PF,而非18PF。

在晶振PCB布线设计时,不管是要求外接电容要与晶振进行最佳匹配,电容等值,还是布线尽量短且长度一样等,终极目的只有一个,那就是尽量减少外界对晶振输出频率精度及稳定性的各种可能性干扰。

pcb布线注意点:晶振

7 相关测试

无源晶振怎么测试?用X10档跟交流耦合进行测试。

无源晶振怎么测试?

•晶体频率不能直接用示波器测量,因为测量分辨率通常不足以将频率偏差计算到几个ppm以内。必须使用频谱分析仪或频率计数器(使用稳定的10MHz参考)来测量频率。

•晶体频率不得通过直接探测XI或XO引脚进行测量。以任何方式加载这些引脚不仅可以改变频率,还可以停止振荡晶体。频率必须始终通过查看诸如引脚之类的导出时钟信号来测量。例如,在-Q1上,这是引脚16。还可以通过使用IEEE测试模式2来测量频率漂移,这是本地时钟的良好表示。

•匹配电容器微调

离散负载电容器CL1和CL2必须针对每个新的板设计进行优化,因为晶体电路的布局因板而异,这将主要影响值。上述描述的过程可用于选择离散负载电容器的初始值。一旦电路组装在电路板上,就必须测量实际的晶体频率。如果测得的频率高于预期或要求,则增加离散负载电容的值。同样,如果频率低于要求,则减小离散负载电容。

晶振供应商测试案例1

项目DSP上的25MHz晶振,其负载电容9pF,最高温度才85。

供应商给的报告有频率偏差为-27.93ppm(这个值由上面公式可知要先测得谐振频率,然后跟标称频率25M一起才能计算出来,不过供应商通常都只给计算结果,没给测得的谐振频率,但从负值可以看出来谐振频率是偏低了,因为实际负载电容偏高了)

另外也给出了单体自身频率偏差FL,则得到频率相对偏差为-27.93-0.84=-28.78,没超规格书要求

同时还要注意消耗功率,规格书给出最大值一般为100uW。

最后一点串联谐振电阻Rr,一般要求|-R | /Rr >10,以下其实都是符合的。

根据结论更换为,负载电容为12pF,最高温度为105

测试案例2

MCU上使用的40MHz晶振,正常来说,芯片的规格书对晶振两端的匹配电容应该不会有什么要求才对,如下是nxp的S32R规格书,仅仅推荐使用负载电容8pF的晶振。

原本上面用的匹配电容为12pF,而晶振要求的负载电容就为12pF,那明显是不符合的,晶振寄生电容最大值为3pF,就算取Cs为5pF,那最小匹配电容也要14pF,最大匹配电容为24pF。

这里供应商的匹配报告中匹配电容为12pF时,实测负载电容值为8.95pF,即杂散电容约为3pF。

所以当换为15pF时,负载电容计算应该为7.5+3=10.5,实测为10.51。

此时接近12pF了,供应商觉得可以了,实际上如果再改为18pF,那么9+3=12pF应该会更完美吧。

另外他也建议换CL=8pF的晶振,匹配电容为10pF,那么5+3=8pF。当然也是可以的。

同样这里只给出了频率偏差为38.88ppm(没给谐振频率),单体自身频率偏差FL为4.53,则频率相对偏差为38.88-4.53=34.34ppm;换了匹配电容后,频率相对偏差为12.72 。符合规格书15ppm要求。

最后一点串联谐振电阻Rr,一般要求|-R | /Rr >10,以下其实都是符合的

8 参考链接

晶振匹配方法

晶振负载电容和谐振电容的计算方法

水晶工作原理介紹GD.PDF

for PHY.pdf