xilinx时钟问题 IBUFG

时钟问题 之前用没有什么问题,都是直接连接上的,

我在平台上做DDR2,需要200m的时钟信号,我就用DCM倍频了一个,直接接在DDR2的上面,出现了如下错误,请大神指点一二,不胜感激!!

ERROR::770 - IBUFG

'/_inst/.' and

BUFG '/' on net '' are lined up in .

of the same be in .

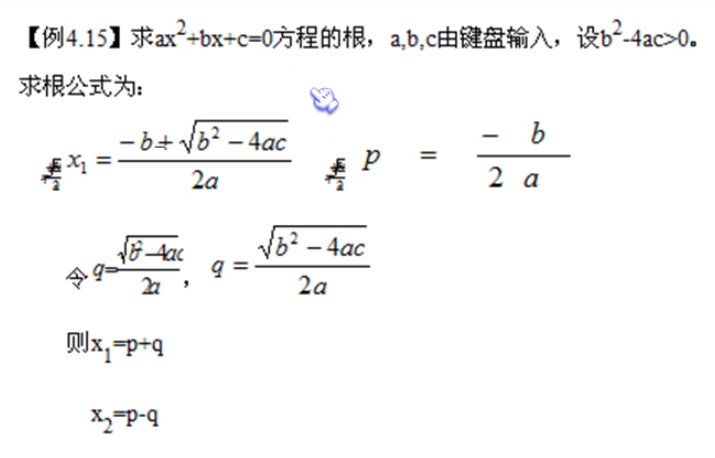

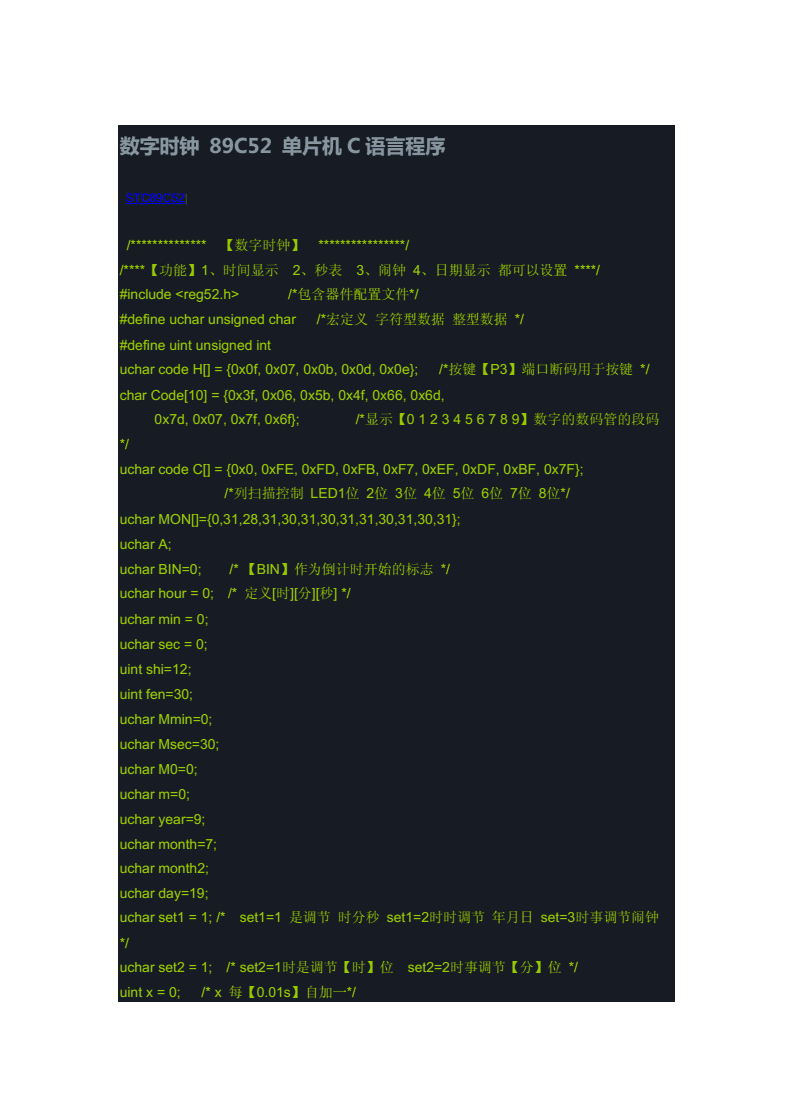

我的程序代码如下:

//**** PLL产生时钟信号

t(

.(clk),

.(),

.(),

. ()

);

然后我直接把给了DDR2的系统时钟信号,如下图所示(DDR2代码太多,简单一个链接):

.(),

这样会出现问题,不知道怎么解决了呢?

之前测试DDR2的时候,我是把外部的时钟直接接在DDR2的上面,用的是150M的时钟,现在板子上面只有一个50M的时钟了,只能自己用DCM倍频了,应该是可以通过一个原语解决的,但是不知道是哪个?我胡乱测试了一下,都不行。

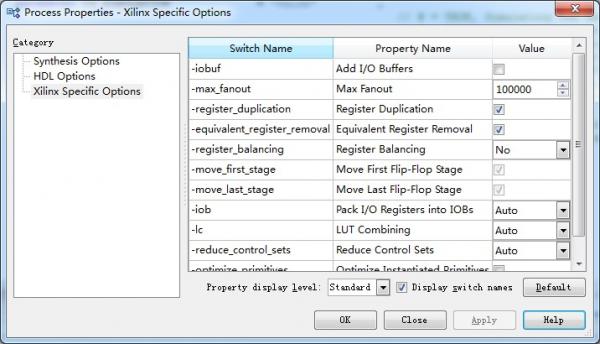

我用的是.7的版本,也尝试设置了XST的这项设置,去掉Add I/O 但是没用。

问题解决,我首先尝试修改PLL的源代码,把下面代码注释掉

BUFG

(.O (),

.I (clkfx));

换成 = clkfx ;

编译之后,会报错,多驱动问题的错误,我就又恢复原装,尝试修改DDR2的源码!!

= ;

//

//(

// .I(),

// .O()

// );

把上面的代码注释掉,然后换成

= ;

大功告成,编译就没问题了!!