计算机组成原理复习题 --- 全面版

1、指令和数据都放在内存上,如何从时间和空间上区分他们是指令还是数据?

答:一般来讲,取指周期中从内存读出的信息流是指令流,它流向控制器;而在执行器周期中从内存读出的信息流是数据流,它由内存流向运算器。

1.数据区分两种,一种是栈数据,和堆数据,

2.而全局变量和静态变量和常量字符串放在文本区或者叫全局区,

3.并在文本区的隔壁还有一个是指令区,专门放指令。

他们分别有一个段基址寄存器指向他们的。所以怎么之别是不需要你来关心的,而是由操作系统和进程tcb块来管理。

2、现代计算机系统如何进行多级划分?这种分级观点对计算机设计会产生什么影响?

答:现代计算机系统可分为五个层次,第一级是微程序设计级;第二级是一般机器级;第三级是操作系统级;第四级是汇编语言级;第五级是高级语言级。

3、计算机实现浮点数乘除的步骤有哪些?

答:实现浮点数乘除的步骤 : 阶码加减; 尾数乘除; 格式化; 舍入处理; 检验是否溢出。

浮点乘除法的运算步骤 :

①阶码运算:阶码求和(乘法)或阶码求差(除法) 即 [Ex+Ey]移= [Ex]移+ [Ey]补 [Ex-Ey]移= [Ex]移+ [-Ey]补

②浮点数的尾数处理:浮点数中尾数乘除法运算结果要进行舍入处理。

例题:X=0 .*211,Y=0.*2-10,求X※Y

解:[X]浮: 0 1 010 [Y]浮: 0 0 110

第一步:阶码相加: [Ex+Ey]移=[Ex]移+[Ey]补=1 010+1 110=1 000 1 000为移码表示的0

第二步:原码尾数相乘的结果为: 0 110

第三步:规格化处理: 已满足规格化要求,不需左规,尾数不变,阶码不变。

第四步:舍入处理: 按舍入规则,加1进行修正 所以 X※Y= 0.※2+000

4、什么是指令周期?机器周期?时钟周期?三者之间关系如何?

答:时钟周期:

时钟周期也称为振荡周期,定义为时钟脉冲的倒数(可以这样来理解,时钟周期就是单片机外接晶振的倒数,例如12M的晶振,它的时间周期就是1/12 us),是计算机中最基本的、最小的时间单位。

在一个时钟周期内,CPU仅完成一个最基本的动作。对于某种单片机,若采用了1MHZ的时钟频率,则时钟周期为1us;若采用4MHZ的时钟频率,则时钟周期为250us。由于时钟脉冲是计算机的基本工作脉冲,它控制着计算机的工作节奏(使计算机的每一步都统一到它的步调上来)。显然,对同一种机型的计算机,时钟频率越高,计算机的工作速度就越快。但是,由于不同的计算机硬件电路和器件的不完全相同,所以其所需要的时钟周频率范围也不一定相同。我们学习的8051单片机的时钟范围是1.2MHz-12MHz。

在8051单片机中把一个时钟周期定义为一个节拍(用P表示),二个节拍定义为一个状态周期(用S表示)。

机器周期:

在计算机中,为了便于管理,常把一条指令的执行过程划分为若干个阶段,每一阶段完成一项工作。例如,取指令、存储器读、存储器写等,这每一项工作称为一个基本操作。完成一个基本操作所需要的时间称为机器周期。一般情况下,一个机器周期由若干个S周期(状态周期)组成。8051系列单片机的一个机器周期同6个S周期(状态周期)组成。前面已说过一个时钟周期定义为一个节拍(用P表示),二个节拍定义为一个状态周期(用S表示),8051单片机的机器周期由6个状态周期组成,也就是说一个机器周期=6个状态周期=12个时钟周期。

指令周期:

指令周期是执行一条指令所需要的时间,一般由若干个机器周期组成。指令不同,所需的机器周期数也不同。对于一些简单的的单字节指令,在取指令周期中,指令取出到指令寄存器后,立即译码执行,不再需要其它的机器周期。对于一些比较复杂的指令,例如转移指令、乘法指令,则需要两个或者两个以上的机器周期。

通常含一个机器周期的指令称为单周期指令,包含两个机器周期的指令称为双周期指令。

5、在寄存器-寄存器型,寄存器-存储器型和存储器-存储器型三类指令中,哪间最长?哪类执行时间最短?为什么?

答:寄存器-寄存器型执行速度最快,存储器-存储器型执行速度最慢。因为前者操作数在寄存器中,后者操作数在存储器中,而访问一次存储器所需的时间一般比访问一次寄存器所需时间长。

6、主存和cache(高速缓存存储器)之间的映像方式有哪几种?

答:1. 直接映像

采用直接映像时,Cache的某一块只能和固定的一些主存块建立映像关系,主存的某一块只能对应一个Cache块。直接映像的优点是硬件简单、成本低;缺点是不够灵活,主存的若干块只能对应惟一的Cache块,即使Cache中还有空位,也不能利用。

2.全相联映像

采用全相联映像时,Cache的某一块可以和任一主存块建立映像关系,而主存中某一块也可以映像到(2ache中任一块位置上。由于Cache的某一块可 以和任一主存块建立映像关系,所以Cache的标记部分必须记录主存块块地址的全部信息。例如,主存分为2n块,块的地址为n位,标记也应为n位。 采用全相联映像方式时,主存地址被理解为由两部分组成:标记(主存块号)和块内地址。CPU 在访问存储器时,为了判断是否命中,主存地址的标记部分需要和Cache的所有块的标记进行比较。为了缩短比较的时间,将主存地址的标记部分和Cache 的所有块的标记同时进行比较。如果命中,则按块内地址访问Cache中的命中块(其标记与主存地址给出的标记相同);如果未命中,则访问主存。

全相联映像的优点是灵活,Cache利用率高。缺点有两个:一是标记位数增加了(需要记录主存块块地址的全部信息),使得Cache的电路规模变 大,成本变高;二是比较器难于设计和实现(通常采用“按内容寻址的”相联存储器)。因此,只有小容量Cache才采用这种映像方式。

3.组相联映像

组相联映像方式是介于直接映像和全相联映像之间的一种折中方案。设Cache中共有m个块,在采用组相联映像方式时,将m个Cache块分成u组(set),每组k个块(即m=u×k),组间直接映像,而组内全相联映像。所谓组间直接映像,是指某组中的Cache块只能与固定的一些主存块建立映像关系。

7、在设计指令系统时,通常从那四个方面考虑?

答:给指令系统确定一个统一的衡量标准是很困难的,但是在一般情况下, 指令系统应满足 以下几个基本的要求:

1.指令系统的完备性 指令系统的完备性是指在使用汇编语言编制程序时, 指令系统应提供足够丰富的指令,以便于编程时选用,即要求指令系统的指令丰富、功能齐全和使用方便。完备性是一个基本 原则,一般来说,一个完备的指令系统应包括前面提到的那几种类型的指令。

2.指令系统的有效性 有效性是指该指令系统所编制的程序能高效率的运行。

所谓高效率主要表现在执行速度快、占用存储空间小两个方面。有效性是一个很复杂的问题,它与完备性是密切相关的,一 个功能齐全的指令系统必定会有高的有效性。如目前许多计算机中增设的数据转换指令、字 符串操作指令等,这些无疑会大大提高指令系统的有效性。

3.指令系统的规整性 指令系统的规整性包括指令的对称、均匀,与数据格 式一致等特性。 指令的对称是指所有的数据存储单元(如寄存器、主存单元等)被指令系统同等对待,所有的指令都可以使用各种寻址方式;指令的均匀是指同一种操作性质的指令,可以支持各 种不同数据类型和不同字长的运算。例如,加法指令能支持不同数据类型(如定点数、浮点 数、十进制数等)和不同字长(如字节、字和双字,甚至四倍字)的运算;指令格式与数据 格式一致是指指令长度与数据长度有一定的关系,以利于存取和处理。指令长度一般取字节 的整倍数,数据长度则取字节的 1、2、4 或 8 倍不等。

4.指令系统的兼容性 不同的机器结构,指令系统不同。但同一系列的机型 则具有相同的基本结构和共同的基本指令集,故指令系统是兼容的。由于系列机中不同机型推出的时间先后不同,结构和性能 上存在着差异,不可能做到全部软件兼容。通常在高档机上可以运行低档机的软件,而在低 档机上则不一定能运行高档机的软件,因此称为“向上兼容”。

8、同步通信与异步通信区别?

答: 1.同步通信要求接收端时钟频率和发送端时钟频率一致,发送端发送连续的比特流;异步通信时不要求接收端时钟和发送端时钟同步,发送端发送完一个字节后,可经过任意长的时间间隔再发送下一个字节。

2.同步通信效率高;异步通信效率较低。

3.同步通信较复杂,双方时钟的允许误差较小;异步通信简单,双方时钟可允许一定误差。

4.同步通信可用于点对多点;异步通信只适用于点对点。

9、什么是程序的局部性原理?

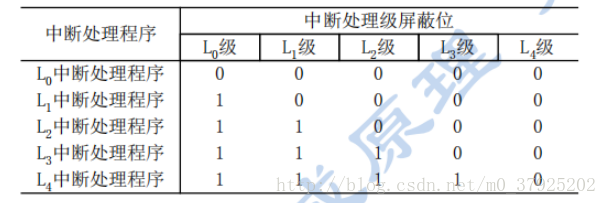

10、某机有五个中断源,按中断响应的优先顺序由高到低为L0,L1,L2,L3,L4,现要求优先顺序改为L3,L2,L4,L0,L1,写出各中断源的屏蔽字。

答: